#### Embedded Systemy

## Introductions.

#### Unit-I

#### . What is an Embedded System

An embedded Syttem is an electronic/electro-mechanical Syttem designed to Perform a specific function and is a combination of both HIWE firmware (software)

Every embedded system is unique, and the hIW as well as the firm ware is highly specialised to the application domain.

EMBEDDED Systems Vs General Computing Systems

Embedded System General Purpose Computing System 1) A System which is a combination of (1) A System which is a combination of special a generic Hlw and a General Purpose hiw & embedded Purpose operating System for executing a gariety of application as for executing a specific Set of applications 2) Contain a General Purpose (2) May or May not contain operating System (GIPOS) an operating system for functioning 3) APPLICATIONS are attendie (programmable) by the user 3) The framware of two embedded Syttem is poe-(It is possible for the end wer to de-Install the operating system Programmed and it is non-alterable by the and also add or demove user end user applications. (4) Performance is the key deciding (4) Application-specific factor Porthe Selection of the requirements (Like System. Always, Foster is Better Performance, Power, Memory usage, etc) are the key

deciding fectors

# Greneral Purpose Computing System

## Embedded Syften

- Less not at all tailored towards & Highly tailored to take reduced operating power lequireyent options for different levels of Power Manageyent.

- Response requirements on not (6) time - (ritical

- Need not be deterministic 99  $\bigcirc$ execution behaviour

advantage of the Power Saving Modes supported by the HIW and the operating system

- 6) For costalis Calegory ofembedded Systems like million contion systems, the response time requirement is highly Critical.

- 7 Execution behaviour PS deterministic for Certalis types of embedded Systems like

Hard Read Time Systemy

#### History of Embedded. Systems

modern embedded System is the -> 1) The flast recognised Apollo Guidance Computer (AGC) developed by the MIT Instrumentation Laboratory for the lunar expedition. They ran the Intertial guidance systems of both the Command Modele CCM) & Lunar Excursion Module (LEM) The Command Module was designed to encircle the moon while the Lunar Module and its crew were designed to go down to the moon surface and land there Satoly engack-around the wrote

Lunar Module and featured in total 18 engines There were 16 reaction control thruster, a descent engine, ascent engine

- The descent engine way 'designed to ' provide thrust (2)

to the lunar module out of the lunar orbit & land

it safely on the moon.

thrust-push

- >MITI'S Oxigenol design was based on 4x words of fixed Memory CRead only Memory) and 256 words of exasable Memory Crandom Access Memory).

- → By June 1963, the figures reached 10 K of fixed and 1k of exacable Memory. The final configuration was 36 K words of fixed Memory and 2K words of exacable Memory.

- The clock frequency At the first Microchip Proto model used in AGC wey 1.024 MHz and Pt way desiled from a 2.048 MHz Coyster Clock.

- The computing unit of AGIC Consisted of 2 11

Instructions & 16 bit word logic. Around 5000

Ics (3-Input Nor gates, RTL Logic) Supplied by

Fairchild Semiconductor were used in this design.

- -> The user groterface unit of AGCP3 known as DSKy

Collsplay/keyboard). DSKy looked like a Calculator.

type keypood with an array of numeraly.

- The first man Produced embedded System was the guidance computer for the Minuteman-I missile in 1961. It was the Autonotice D-17 guidance computer, built using discrete transistor logic & a Hard-disk for Main Memory.

The first IC okt was produced Pry Septembel but computer using them didn't begin to appear until 1963.

# Classification of Embedded Systems.

Based On generation

2) complexity and Performance organizements.

(3) Based on deterministic behaviour > Hard Red Mine 475 lears

Based on triggering REVent Triggery & soft Red Time Systems The classification based on deterministic System fehaliour.

task execution fehaviour for an embedded system Combe either deterministic or non deterministic.

Based on the execution behaviour, Feat Time embedding Systems are Classified Into Hard & Soft.

Reactive systems can be either event triggered or thre triggered.

classification Based on Greneration

FPEST Generation,

The early embedded systems were bull around 8-bit uprousors like 8085 & 280 & 4-bit UC. Simple In the city with formware developed in keypady, Aepper Hotor Assembly code Digital telephone control unit etc.

Second Generation! The embedded Systems are built around 16-bit Leprocessors of 80x 16 bit LC. The Instruction Set for the Second generation Processors Controllers were much more complex and powerful than the first Generation Processors Controllers & Generation Systems.

Thered Generation: With advances on processor technology,

embedded Systemy developers Started making use of powerfup

32 bit processors & H-bit Mc for their delign.

A new concept of application of domain specific Processors/ Controllers Like Digited Signal Processory (DSD) & Application Specific Jutegrated Clouds (ASICS)

The first rudion set of processors belowe more complex Expower ful and the concept of Instruction pipelining. Ent Robolics, Media, Industrial process constroil, Networking etc.

Fourth Generation: The odvent of System on chips (soc), reconfigurable processors a Multicore processors are bringing high Performant, light Integration of Ministernisation put the embedded device Market. The soc technique Juplements a total system on a chip by Integrating different functionalities with a Processor core on an Integrated axt.

EN + Smart Phune Levily, Mobile Internet devily

## Classification Based on Comprexity & Performance.

- (1) Small-Scale Embedded Systems. These are usually built around low performance & low cost & or 16 lit lep/ll.

A small-scale embedded System may or may not contains an operating system for its functioning.

- 2 Medium Scale Embedded Systems: There are built around Performance, low cost to or 32-bit up/uc or dsp.

- (3) Large Scale & m bedded Systemy | Complex & ystemy .

The high performance 300x 64 bit PISC Processors /

Controvers or Reconfigurable System On Chip (RSOC)

Or Multi Core Processors & programmonthe Logic

devices. They may Contains multiple Processors / Controlled

Ex co-cavity | Hardware accelerators for offloading

the processing requirement from the main processor

Of the 343 logs.

Decoding/encoding of media, corptographic Auntion Implementation, etc.

Complex embedded Systems usually Contains a high Performance (RTOS) for touse scheduling, Prioritisalis a Management.

- (1) Consumer electronics! Can corders, Congerous, etc.

- (2) Household appliances T.V, DVD Player, washing Machine, fridge, Microwave Over

- 3) Home Automation of Security system: Africanditioners, sprinkless, griticular detection alarms closed act T.V. Camerus.

Ifre alarms etc.

- Engine control ignition systems, automatic navigation systems

- (5) Telecons: Cellular telephones, telephone switches, Handset apprication, etc.

- 6) computer p'eripherals : printers, Stanners, Fan Marching

- Frewally, etc.

- (8) Health Care: Different Kinds of & Count est EFG, ECG.

- (9) Mensieunt & Justrangentation: Digital Multimeter,

digital CROS, logic analyzery PLC Systems, etc.

- (10) Banking & Retain: Automatic teller Machines (ATM) & Currency counters, point of Jaly CPOS

- (1) Card Readery: Bar code, Smoort Card readers, handheld devices, etc.

## Purpose of Embedded Systemy-

Each embedded System Is designed to serve the Purpose of any one or a Combination of the following today.

- 1 Data collection | Storage | Representation.

- Data communication. 3 Data (Signal) Processing @ Monitoring

- (S) control (6) Application specific user futerface.

#### 1 Data Collection / Storage / Representation

The term "data & refer & allicinds of Antormation, Viz, texts

where term "data & refer & allicinds of Antormation, Viz, texts

Data Can be either analog (Continuous) or digital (discrete).

Embedded Systems with analog data capturing techniques

collect data directly by the form of analog Signaly

where as embedded Systems with digital data collection onechanism convoits the analog signed to corresponding digital Signed using analog to digital (AD) converter and they collects the finary equivalent of the analog data.

Embedded Systems designed for pure applications without storage, used by control of snstrumentation, collect data.

Some Systems sncorporate a built - 90 | plug -90 storage.

memory for storing the aptured data.

Some Statemy are representative of the collected data by william (graphical quantitative) or audible Meany cusing display unity (ICD, LED, etc]; buzzers, alarms, etc.

En: Measurphy Instruments with storage Memory

Gi Movitorphy Instruments with storage Memory was in

Medical Applications.

A dighted Camera is a typical example of an embedded system with date Collection/ Storage/ sepre-

#### Data Communication

Embedded data Communication System one deployed by applications surging from complex Satellite Communication systems to simple thome Nwking Systems. The data collected by an embedded telminal may require transferring of the Same to some other systems localed remotely.

The transmission is achieved either by a wire-line medium or by a wire-len Medium.

A wireless Medium offers Cheaper connectivity solutions and make the Communication Link free from the house of.

Data can either be transmitted by analog or digital.

Modern Industry toends are settling towards digital communiction.

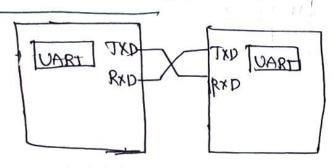

The data communication unity to like wireless Modules

(Blue tooth, Zigbee, Wi-FI, EDGE, GPRS, etc) or Wire-line

MUdules (R3-232C, USB, TCP|IP, PS2, etc).

Cootain embedded Systems art as a dedicated transmittion unit flw the sending of peciving telminals, afforing sophisticated functionalities like data parketising,

encrypting & decrypting. Letwork hubs, volues, & switchy etc. are typical examples of dedicated data transmissions embedded Systems.

#### Data ( signal) Processing.

The data (voice, timoge, video, electrical signal) collected by embedded systems may be used for various kinds of data processing Embedded systems with signal processing functionallity are employed for applications demanding signal processing like speech coding, synthesis, audio video adec, transmission application, etc.

En: Adigital bearing and simproves the hearing apacity of bearing speech persons.

#### Monitoring

All embedded products coming under the medical domains Care with monitoring functions only. They are used for determining the state of some variably wing imput sensors. They cannot surpose control over Jeviables.

the heart best of a patient.

The machine is sortended to do the munitaring of the heart beat. It count Impose Control over the heart beat. The sensors wed for ECG are the different electrodes connected to the patient & body.

Ent Digital CRO, digital Multimeter, logic analyzers

(ontrol & Instrumentation application. They are used to

current, Voltage etc.

Embedded Systems with Control functionalities Ample control over some coariables according to the changes PN Input Variables.

A system with control functionality controls both sensors of actuators Sensors are consected to the Input Port for Capturing the changes Pn environmental Variable or measuring variable.

The actuatory Connected to the Olp Port are controlled according to the changes pro Plp Gariable to Put an Ampart on the controlling Gariable to bring the controlled Cariable to the Specified Dange.

APT conditioner systems used Por our home to control the rooms temperature to a specified limit is a stypicy example. for control purpose.

An air conditioner contains a room temperature Sensing element. (Sensor) which may be a thermistor & a handheld unit for Setting up (feeding) the desired temperature.

The handheld Unit may be connected to the Central embedded unit ruiding Inside the air conditioner through a wireless link or through a wired link.

The compressor unit city by the advantor.

The compressor is controlled according to the current room temperature and the desired temperature set by the end user.

The Input variable is the current room temperature. and the controlled Jewiable is also the room temperature. The controlling comiable is cool air flow by the comprehor unit. If the controlled variable and the variable are not at the fame value, the controlling cariable tries to represent them.

# Application Specific User Interface

These are embedded systems with application - Specific Wer Interfaces like buttons, Switches, Keypad, Lights, bells, display units etc.

In Mobile Phone the west Interface is Provided through the Key pad, graphic LCD Module, System speaker, wibratton about etc

- > Smart Running Show from ADIDAS The Jano Wative Bonding of Lifestyle with Embedded Technology.

- -) Adides launched the Smart durning shoes Pn the market Pn April 2005-

- > The shoe uses a Magnetic sensing system to measure.

Cushioning level, which is adjusted via a digital signal

processing unit that controll a motor-dolver cable system.

A hall effect sensor is positioned at the top of the a cushioning element and the magnet is placed at the bottom of the element.

The curhioning Comprehe on each Impact, the Sensor measury the distance from top to bottom of mid-sole (accurate to O.1 mm). About loop readings [ second are taken and octayed to the Shoely up. The McCroprocessor (MPO) by positioned under the coch of the Shoe. It rung an algorithm that Compary the Comprehen message received from the sensor to a preset range of proper cushioning levels. The MPO sends a Command to a Micro Hotor, howed on the mid-foot. The Micro Hotor turns a lead screw to lengther or shorter a cobbe secured to the Walls of a plastic — cushioning element

A typical embedded system contains a single Chip controlle. which acts as the master brain of the system. The controller Can be a up ( e.g. Intel 8085) or a Mc (e.g. Atmel AT 89(52) Or FPGA (Field Programmable Brote Array) Leverte eg. (XPRON Spattan) or a Digital Signal Processor (DSP) (e.g. Blackfin Processors from Analog Devices) or Application Specific Integrally Cut (ASIC), Application Specific Standard product (ASSP) (e.g. ADE 7760 Sirgle Phase Evergy Metrely IC-Brown Analog Devius for energy metering applications Embedded h/w/SIW Systems are basifully designed to Togulate a physical variable or to manipulate the state of

Some devices by sending some control signals to the Actualors

Desponde to the Plp signaly provided by the end the

or decity connected to the Olp ports of the system, by

to the Plp posts.

The control is achieved by processing the Information coming from the sensors and user Interface and Controlling Some actuators that regulate the Physical Variable.

Key bourdy, push button softches etc are examples for common user Interface PIP devices where as LEDS, LCDS, Pie 30 electric buzzers, etc are of devices.

The sensor Information is passed to the Processor exter signal conditioning & digitisation. Upon receiving the sensor addar. the Processor or boain of the embedded System Performs, some Pre-defined Operations with the help of the firmware embedded in the system and sends some actuating signals to the actuator connected to the Olp port of E.S., which in turn acts on the controlling variable to bring the controlled periable to the desired level to make the E.S.

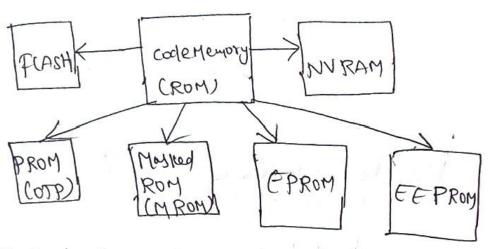

The Memory of the History of responsible for holding the control algorithm of other Important configuration details. ES, the memory for storing the algorithm or configuration data is of fixed type, which is a kind of ROM

The Memories are OTP, PROM, UVEPROM, EEPROM GEPLASH.

Random Accent Memory (RAM) Is used by most of the Systems as the working memory. Various types of.

RAM Like SRAM, DRAM & NVRAM.

The controller - Based embedded System, the controlled may contain Internal Memory for Storing the Control algorithm and it may be an EEPROM OF FLASH Memory

8

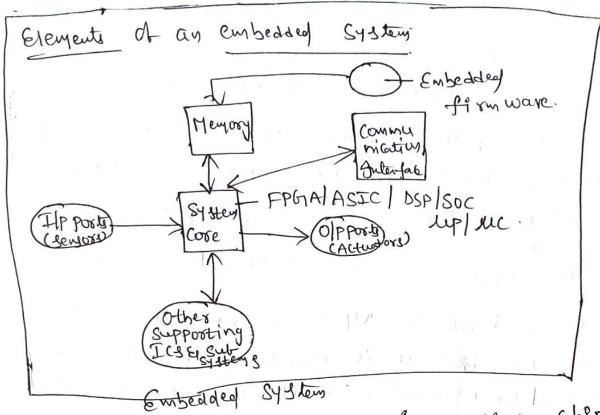

Embedded Systems are do main & application specific & are built around a central core.

- (1) Mecro processors (1.2) Microcontrollers (1.3) Digital

Signal Pro Conors.

- (2) Application Specific Integrated Circult & (ASI(1))

- (3) Programmable Logic Devotes (PLDS)

- (4) commercial off the Shelf Components (COTS).

General Purpose & Domain Specific Processors.

Microprocenses: A up 13 a silicon chip representing a CPU, which is apuble of performing a situmetic as well as logical operations according to a predefined Set of Justructions, which is specific to the Manufacturer. Working The CPU contains the ALU, control unit and it requires the Combination of other HW lake memory, themer unit, Interrupt controller.

Interrupt controller.

Intel claims the Credit for Leveloping the first lip unit

Intel 4004, a 4-bit Processor which was released Pn Nov 1971

It featured 1k data Memory, 19-bit Program Counter &

4k Program Hemory, Sixteen 4-bit general Purpose registers

& 4b Instructions. The clock speed of 740 kHz. In 1972

14 More Instructions were added to the 4004 Instruction

Set 4 the Program space is upgraded to 8k.

Also gotersupt Capabilities were added to and it renamed as

Intel 4040. It is suplaced in April 1992 by Intel 8008

Which was similar to Intel 4040, the only different was

that its po was libilit wide and the 8008 Sorved as a

terminal counter controller.

In April 1994 Antel launched the fryst 8-bit processor

the Intel 8080, with 16-bit addrew Bus & program Counter

and Seven 8-bit segisters (A-E, H,L: BC, DE & HL) pairs

formed the 16-bit segister for this processor)

Intel 8080 Was the most Commonly used processors for snowstrial control & embedded applications in the 1925.

Intel 8080, Motorola also entered the market with their processor, Motorola 6800 with a different architecture & Anstruction Set Compared to 8080.

In 1976 Intel ame up with the upground version of fosto.

Intel 8085, With two newly added Instructions, three Interrupt

Pins & Serial Ilo. Clock generator & bus controlled cets

were built-in & power supply part was modified to a

Single +5 V Supply.

In July 1976 Zilog entered the up Market with its Z80

Processor as competitor to Intel > Motorolla 6800 - Different to 8080

Architecture Set Compared to 8080

In 20th century 16,324 64-bit processors Come Anto the place of conventional 8-bit processors. Today processors with clock speeds up to 2.4 GHZ are available in the Market, Not

Intel, AMD, Freescale, IBM, TI, Cyrix, Hitachi, NEC,

LSI Logie. etc are the key playor in the processor

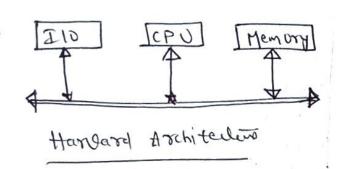

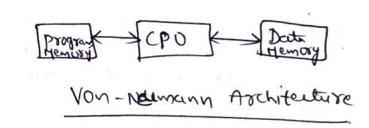

Harvard Architecture Contains Seperate buses for Program (9)

memory Ex Data Memory, where as processors based on

Von-hermann architecture Shares a Single System bus for

program & data Memory.

Reduced Instruction set computing (RISC) of Complex Sustruction Set Computing (CISC) are the two Common & Instruction Set Architectures (ISA) available for Processor design.

#### Intel Microprocessory

| Microbadonona            | Year of<br>Introduction | Data BW<br>Width<br>(Bit) | Address<br>Bus width<br>(Bit) | Memory<br>S1Ze                                 |

|--------------------------|-------------------------|---------------------------|-------------------------------|------------------------------------------------|

| 4004<br>8085A<br>8086    | 1971<br>1976<br>1978    | 8 16                      | 10<br>16<br>20                | 1KB<br>.64KB<br>1MB                            |

| 8088                     | 1980                    | 8                         | 20<br>20<br>20                | 1MB<br>1MB<br>1MB                              |

| 80188                    | 1982                    | 8<br>  16<br>  16         | 24                            | 16 HB Red, 46B                                 |

| 803868X                  | 1984<br>1985<br>1989    | 16                        | 26                            | 16 M B                                         |

| 80389 DX<br>80\$89 DX SX | 1986                    | 32                        | 32                            | 46B+8KB) KKB<br>Gashe.                         |

| Pentium ovel             | 1993                    | 64                        | 32                            | 46B+16KB Gacke                                 |

| Dentium Pro              | 1995                    | 64                        | 36                            | 649B+16KB4 Gashe                               |

| PentilumI                | 1997                    | 64                        | 36                            | + 256 K BL2 Cache<br>6467B+32xB4 Cache         |

| Pentlum -II              | Xeon 1998               | 164                       | 36                            | 646B+32KB4                                     |

| Dentium-I                | II 1999                 | 64                        | 36                            | Cathe +256KBL2  Coushe  Coushe  Coushe  Coushe |

| Postium 4                | 2000                    | 164                       | 36                            | 649B + 324B L+ Cache                           |

#### Motorola 68000 Family

| In In                   | C 6800 .    | M C 68020                              | MC 68030   | Mc 68040     | MC68060         |

|-------------------------|-------------|----------------------------------------|------------|--------------|-----------------|

| MIPS 1                  | 2.4         | 6.5                                    | 1          | 3 9          | 7100            |

|                         | _           | 0.25                                   | 5          | 3.2          | 12              |

| MFLOPS<br>Address Ronge | 16 M by les | 46 Bytes                               | 4 Co Bytes | Lights       | 46 Bytes        |

| Data Buy                | 16-bit      | 32-bit                                 | 32-bit     | 32-bit       | 32-bit          |

| clock MHz               | 8-16        | 16-33                                  | 16-50      | 25,3340      | 50-66           |

| I-Cache                 | _           | 256 84 65                              | 256 BHO    | lex Bytes    | Sk Byles        |

| D- Cach e               | - 12 11     | · —                                    | 256 Byte   | Es Cak Bates | 81c Bytes.      |

| Burst Fill              | 11/20 6 .   | 10 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | H Byte ठी  | w 16 Ryte o  | IN 16 Byte olw. |

| on cyto who             | - 1         | - v h                                  | Yes        | Yes          | . Yei           |

| FPO                     | 68881       | 68881                                  | 68882      | - on-chip    | ourchip.        |

General purpose Procenor (Grpp) Vs. Application - Specific

Instruction Set Processor

The General Purpose processor Contains an ALU & Control Unit (Co)

Application Specific Justisention Set Processory (ASIPS) are processors

With architecture & Justisention Set optimized to Specific dancies/

applications Jeans Demonstrative NIW Processing, automative, teleson,

Media applications, digital Stand Possessing, control

applications.

ASIP = Processor ton chip peripherals

ASIPS first e architectural Spectrum SIW GIPP VS

ASICS.

-> Gpp 1y Pentlum 4 AMD Athlon,

> MC 13 Automative AVR, USB, AVR from Atmed Digital Signer

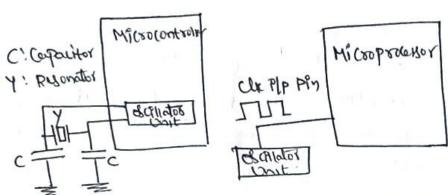

Micro Controllers: A Microcontroller is a highly Integrated chip that contains a CPU, Scratch Pad RAM, special of general Purpose register arroys, on thips Romperson Memory for program storage, limer of Intersupt Control Units and Societas Ilo Porty Micro Controllers and the considered of a Super Set of supposenors in quantitatively pulcased Ilo Porty Texas Intermet to Intermed to provide Morrish Intermet to pulcased Intermet to Intermet to pulcased Ilo Porty Intermet to Intermet to Intermet to Intermed Intermet to Interm

In 1977 Inter antered the UC market with a family of controllers coming under one umbrella named MCS-48.

The processors came this family were 8038HL 8039HL 8049HL 8048H, 8049H & FOLTO AH.

Intel 8048 is recognised as Intel's first MC and it was the most prominent member in the MCS-48TM.

The sold procession ferrind 8048 was Poiechild's F8 lip & Intel's good of Leveloping a low cost & small size process.

The 8011 processor cores are used in more than 100 decision by More than 20 Independent manufacturary like Morein, philips, Atmel etc. under the livense from Intel.

Our cost, wide associal libiting, Memory effectent furtraction sep, Booken processing Gefability.

The PIC family Mc From Microchip Jechnologica. It is a thigh proformant RISC Mc Complementing the CIUC. Intereson, Freescale, Philips, Atmel, Maxim, Microchip or The 16-bit applications by developing the Philips XA (extendened Architecture) Mc feeler.

Wickobaorona Or wices controller Microprocessor M 9( ocontroller: DA SI I'CON Chip & epowenting a 1) A Me is a highly Integral of chip that contains a cpu, Central Processing Unit CGPU) which is apable of performing. Scrotch pad RAM, Special of genery Purpose register arrays, on chip arithmetic as well as logical ROM/ FLASH memory for operations according to a pre-Program Storage) timer & defined get of Just rutions Interrupt Control Units Ex 2) It 13 a dependent unit. dedicated Flo Purk It requires the combination @ It is a sey-contained Unit of other chips like limere and it does it require external program & datamemory Interoupt controller, timer Chips, Intersupt controller. UART, etc. for ly functioning etc. for functioning. 3) Mostly application - Orlented or (3) Most of the sime general domain-Spelific. purpose Pridesign & operation 4) Doesn't Contain a full most of the proumory contains Multiple full - PM Ito Posty which In Ito port. The Iloport an the operated as a single 800 16 Runchinality needs to be Suspleyented with the help of or 32-bit port or as Individual

port Ping.

1) Tangelist for confedded manust

where Performance is not so .

Cof Hay.

external ppI chips like \$255

wentet where pestormance

( Tangelia for high end

is Surportant.

| Mecroprocenor.                                 | MP (ro controller.           |

|------------------------------------------------|------------------------------|

| Limited Power Saving options<br>Compared to MC | Includes lot of power sawing |

Dighter Signed processors. DSP & are powerful special purpose.

8/16/32 bit uprocessors designed specifically to west the.

Computational demands & power constraints of todays & embedded and v, video & communications applications. Digital Signed.

Processors are & to 3 times faster than the general purpose.

Approcessed in Signed processing applications.

by DSP to Procen the data.

Data Memory: Working Memory for Storing temporary veriables & delta I figured to be processed.

Computational Eagine: This Incorporates many Specialised a withmetic units of Cach of them operates Simultaneously to Increase the execution speed. It also Incorporates multiple. HIW Shifter for Shifting toperates of thereby savey execution time.

DSp. It is responsible for Explaining Signals to be processed & delivering the processed Signals

Ent Audio video esonal processing, telecommunicating & Multimedia appelaceture are typical examples where DSP is employed.

Display Signay Possessing employs a large a mount of seat-time Collembration. Sum of products (Sop) Collembration, Consodulton, FFT, DFT, etc. are operations performed by. DSP.

Blackfor processes from Analog Devokes is an example of DSP which deliver break through Signed - processing Performance & power Cythruny a full 32-bit RISC MCV programming Model. These processory present high - Performance, homogeneous SIW Tangets, which allows flexible octours allowed flexible octours allowed flexible octours allowed time signal processing totally & pon-had time Central Passy.

#### RISC

CISC.

Dlesses Number of Anstructions

- DInstantion Pipelining and Increased execution speed:

- 3) Oothogonal Justiseather Set CAllows each Instruction to operate On any register and age any addressing Mode)

- (4) operations are performed on registers only, the only memory operations are road of store

- (E) A large number de registers are available

- OGreater number of gry toudion

- 2) Generally no Instruction

- 3) Non-orthogonal Antructions

set (All Antructions are

not allowed to operate on

any register and we any

addressing Mode. It is sustaining

Specific)

- @ operations are performed on the Instruction.

- E) Multed Number of General

|            | RISC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CISC.                                                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| A (S       | programmer needs to write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Danstrudions are like mains                                         |

| 4          | more code to execute a lask<br>Since the Instructions are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in Clanguage Aprogrammer aus                                        |

|            | simples ones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | with a sing & Instruction which                                     |

| 1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | In turn provides the effect of using                                |

|            | Extend of the contract of the | RISC.                                                               |

| <b>(1)</b> | Single, fixed length Suprocutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | @ Variable length firstructions.                                    |

| ~          | Less colors was a per court                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | @ More Silicon wage since more additional decoder logic is remisely |

| Ŋ          | en and the respect of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | to Implement the complex In struction                               |

|            | I have the second to the second to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | devoding.                                                           |

| 9          | with Harlard Architectur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Can be Har Ward of Von -                                            |

|            | and a strift of the strip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Neumann Architecters.                                               |

| (01)       | Ent Atmey AVR LLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ENT Almet AVR LLC                                                   |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AT 89C51.                                                           |

# -> Har beind Ms Non- Neumann Procenor | Controller Architecture

| Harvard Architecture                                                                                                       | Von - Neumann Architecture                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Since data Memory & programs Memory are stored Physically Por allferent locations, no chances for accidental corruption of | DSingle Shared by for Justiculton & data fetching.  DLOW performance compared to Harveard architecture.  B cheaper.  Always self modifying coder  Brince data Memory & program  Memory are stored physics in |

| Deodram memora                                                                                                             | Menory.                                                                                                                                                                                                      |

# A Big-Endian V& Little-Endlan Procenors/Controllers

Endianness Specifies the order on which the data of stored on the memory by processor operations on a multibyte System (processors whose word size is greater than One byte) suppose the word length is two byte then data Carribe stored on memory on two different ways

1) Higher order of data byte at location Just below the higher memory

Delower order of Later byte at 10 Cotion just below the Hisnel Memory.

If stored for memory at the lowest address. The Higher-order byte of the data (Comes first).

Base Add +2

Byte 2 Byte 2 0x20002 (Base Add +2)

Base Add +2

Byte 2 Byte 2 0x20002 (Base Add +2)

Base Add +2

Byte 3 Byte 3 0x20003 (Base Add +3)

Base Add +3

> Little - Endian Operation.

Big - Endian

The higher-order byte of the data is stored in Memory at the lowest addrew. The lower-order byte at the highest address (The fig end (omes first).

Buse Addrew + 2

Byte 1

Ox 20002 (Base Addrew + 2)

Byte 1

Ox 20002 (Base Addrew + 2)

Byte 0

Ox 20003 (Base Addrew + 3)

Byte 0

Ox 20003 (Base Addrew + 3)

Big-endian operation

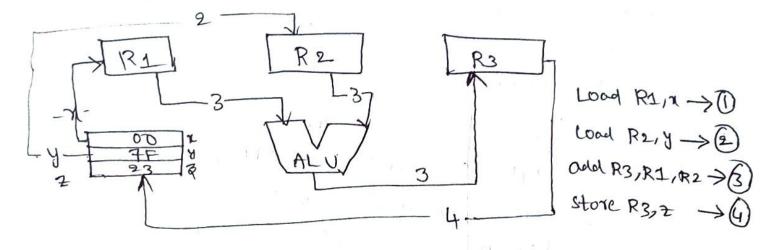

Load Store Operation & Instruction Pipelining-

If the Operand is sperified as Memory location, the content of it is loaded to a register using the load furtheution. The Justraction store story data from a specified righter to a specified Memory to Cation.

The first Instruction load RI, X loady the register RI with the content of M.L. X, the Second Instruction head Re, Y loads the register R2 with the content of M.L. Y.

The Instruction and R3, R1, R2 and the Issa Content of Y egistery R1 & R2 & storey the result in reg R3.

The next Instruction store R3, 2 stores the Content of reg R3 in M.L Z.

The fetch part fetches the Instruction from programy

Memory or code Memory of The decode part decodes

the Instruction to generate the necessary control

Ligner The execute Stage reads a the Operands,

Personny ALU operations and story the result.

If the current Instruction in progress is a programy control flow transfer sustanction like Jump or and Instruction.

whenever the current systruction is executing the PC will be loaded with the address of the next sustantion Incase of Jump or branch systruction, the new location is known only ofter completion of the jump or branch systruction.

PC: program counter.

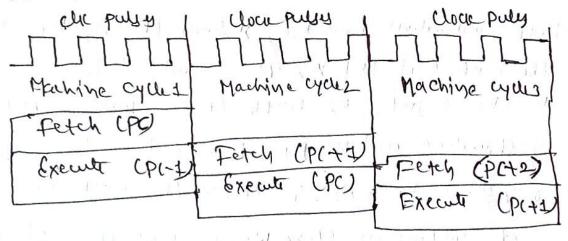

-> The Single - Stage Pipelining Concept.

ASICS is a nickochip designed to perform a specific or unique application. ASICS are propreitary products. As a single chip. ASIC consumes a very small area in the total system and thereby helps in the design of smaller systems with high application of functionalities.

ASIC based 375tem 3 are Positiable only for large Volume Commercial productions. Fabrication of ASICS organises a Nonrefundable Initial Investment for the processor Technology of Configuration expenses. This Investment is known by MRE

(Non- Removing Engineering Cont). Ge it is a one-time Investment.

The NRE is borne by a third parts of ASIC.

The ASIC it offerred to of Application Specific Standard Product (ASSP)

Devices for Energy metaling applications 1's a typicy example for ASSP.

Programmable Logic Devices (PLD'S)

Logic Devises are two Cotegories Offixed & Offogrammable

As the name Indicator, the cuts in a fixed logic device are

Permanent, they perform one fun or let of familions once manufactured, they cannot be changed.

The PLD used for NIW router, a DSL Modern, DVD player, Automotive Navigation system. There are no NRE Gost Et The final design is completed much faster than that of a custom, fixed Logic double.

The PLDS are FPHA & CPLDS.

#### CPLD & PAGAS

The largest FPHA now Shipping, part of the xiling Virtex line of devices; provides eight william & System gates " Line orlative density of logic)

PPGAS are used, for data prouning ap storage, to Suffrage-N, tele communications, a DSP.

CPLDs by contrast, offer much smaller amounts of hostic -up to about 6,000 Grats. But cplps offer very predictable timing characteristics and are therefore Ideal for critical Control applications—

CPLDS 1 by contrast, offer, much smaller amounts of lookup to about 19000 Galos - OPLDS such as the XPLINX

COOI Runner TM sails also & enine extremely low

amount of Power & are very proexpensive, marring them

Adead for cost-sensitive, Battory-operated, portable application

Such as Mobile Phones & digital Handhely aresistants.

# Advantoges of CPLDS

Brown those costs when they disign their programmable doubter.

- Depts offer automers much more flexibility during (15)

the disign cycle because design iterations are Simply a motter

of changing the programming file.

- 3) PLDS don't require long lead times for predaty per or produc-- Utan parts - the PLDs are already on a distributor's

Shelf of ready for Shipment

- > PLD suppliers such as XPlink are fallers' companies on the owning this manufacturing foundaries. XPlinx Outland that lob to partnery like thishiba & UMC. Whose chief occupation is making chips.

Commercial Off-the-Shelf components (COTS)

The COTS Component Itself may be developed a round a general propose or domain specific Processor or Application specific Antigoration act or programmable Logic decline.

COTS products are designed for such a way to provide easy system Gomponents

The examples are COTS How Unit are remote controlled toy Car

Control unit Including the RF Circulary Part, High

Performant, High freq Mich was electronics (2-2006142)

High B.W Ald Converted electron optic IR Imaging enrays

UVIR detectors, etc.

The Processors Controllers contain built in memory q this memory is syound as On-Chip Memory. Others do not contain any memory Incide the Chip and remissy external memory to be connected with the Controller / Processor to Store the control algorithm. It is - Called Off-chip Memory

Program Storage Memory (ROM)

- Dragked Rom (MROM)

- (D) (reation of an enhantement or septetion mode tomor through channel Jusplant.

- By creating the memory an either using a standard townstor or a high trushold towns. In the high threshold made, the supply voltage required to turned on the translator is above the hormal ROM IC Operating addage. This ensures that the truor is always of and the memory and stores always lossed

GHEB GHES GHES GHES GHES SIMPHALES SIMPHALES 4-Telmpron

n-channel MOSFET

4-Telumnay Simplified Simplified P-channel MOSFET.

B-Body ox Substrate.

- RB 6- 1 5- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 15- 6- 4-Telminal simplified simplified

n-channel depletion-type MOSPETS.

Masked ROM 130 good Condidate for storing the embedded firm wan for low cost combedded dellies.

Programmable Read only Memory (PROM) (OFP)

Unlike Masked ROM Memory, One Time Programmable Memory COTP) Or PROM 90 not Pre-Programmed by the Manufacture. The enduser Ps responsible for programming these devices. This Hemory has nichrome or poysition wise assunged in a Nietom. Fusy which are not blown | butned represent a lugic I where as Juses which are problems busined represents a logic or. The default State is logic 1".

# Electrically Exagable Programmable Read only Memory( [EEPROM).

The EEPROM Memory and be altered by using electrical signal of the Degister By te level. They can be loased and Jeprogrammed m-circuit. These Chips Include a chip exase Mode & Inthis mode they can be erased in a few MSec.

FLASH Memory: This is organised as sectors Chocks for Jages.

FLASH Memory stores Information Prian array of Houting gate

MOSFET Transistors. The typical crasable Capacity of FLASH is

1000 cycles.

NVRAM Non-volable RAM is a Tandom access Meyory with battery fackup. It contains static RAM based memory & a minute battery for proceeding supply to the memory in the attende of exteenal power supply.

The litespan of NURAM is 10 years. DS 1644 from Maxim | Dalley is an example of 32 NURAM.

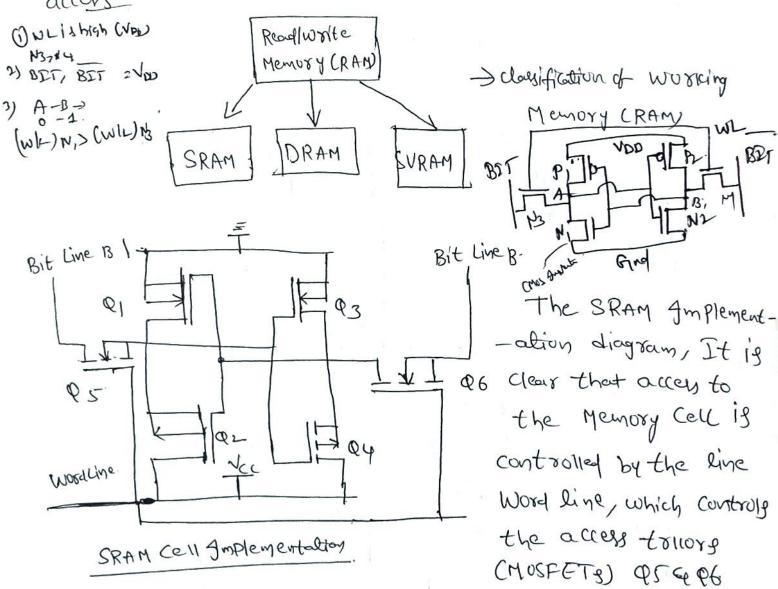

Read-work Memory/Random Access Memory (RAM)

RAM is the Leter Hemory or working Memory of the controller Processor. Eury Dead from it and worker it. RAM is Volatile when the Powel is turned Mb, all the Contents are destroyed.

RAM is a direct actes Hemory, meaning we can acres the Legisled M-L directly without the need for tra versing through the entire M-L to Seach the destreed M-L.

RAM generally falls Into three Colegories; Static RAM, (CSRAM), Jynamic RAM (DRAM), non-Volatile RAM (NVRAM).

#### Static RAM (SRAM):

Static RAM Stores dute Por the form of Voltage They are made up or flfs Static RAM is the fastest form of RAM aboutable SRAM Cell (bit) is realised using 6 Transistors.

(0x 6 MOSFETS) Four of the Truors are used for buriding the loach (flf) part of the Memory cell of two for controlling the accept:

The access transistory controls the Connection to bit lines B Ge B). For woiting 1, make B=1, B1=0,

FOX writing 0, make B=0 & B1=1). Write control PRead Contrul. Dula to write Viguali gation of SRAM cell The Four Transistors por the middle form the cross coupled Inverter. The limitation of SRAM are low apacity of High cost. Dynamic RAM: It stores dolar In the form of charge They are made up of MOS Trillox gates. The advantages of DRAM are Pts high density so lowest compared to SRAM. The Disadvantage Or Information is stored as charge of it gets leaked Off with time of to prevent this they need to be refreshed pertodicaly. SRAM Cell DRAM Cely Made up of 6 CMS TOTIONS D Made up of a MOSFET Word Line Eq a Capacitor CMOSFET) (2) Doesn't reduite refreshing (5) Bedrard retreshing DRAM CELL Amplementation (3) LOW Capacity (Lendenge) (3) High Capacity cttighty dense. 4) More expensive 4 Less expensive

Dels expensive.

Stow in operation

July to represent

sequilement

orthe time is 60mgs write operation is fuster that read operation.

bottery backup. It contains static RAM based memory with bottery for providing supply to the memory in the absence of external power supply. The life span of NVRAM is expedient to be around to years. DSITGH from Maxim/Dallas is an example. for 32 KB NVRAM.

Memory According to the Type of Interface.

- A parallel Interface [The Parallel data lines (DO-DI)for an 8-bit processor | Controller will be connected to DO-DI of two memory.

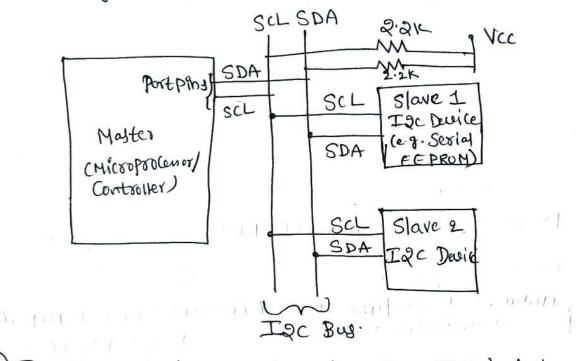

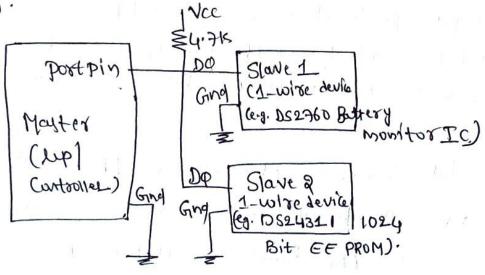

- The serial Interface like IDC (it is a aline sould Interface)

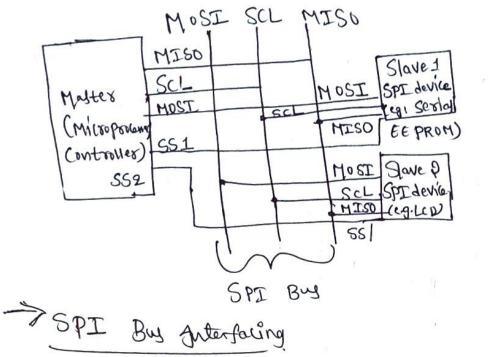

Of It may be an SPI (Scriet peripheral Interface, 2+1)

line Interface whom n stands for the total number of

SPI by devotes in the system).

Atmel corporations AT24C512 for sevial memory with apaulty. 512 toyler & 2-wire Interface.

Member Shadowing

Generally the execution of a program from a ROM is

vory slow (120 to 200 ns) compared to the execution

from a RAM (40 to 70 ns) From the liming Parametery

it is obvious that RAM access by about 3 timy as fast

as ROM access. Shadowing of memory is a technique adopted to

solve the execution speed Problem in Processor-Based Syslems.

In computer Systems & video systems there will be a configuration

LOHING ROM Called Basic Input of O/P Configuration ROMOX Simply BIOS

816 = 65536 by tes = 64kb.

The 2nd parameter that needs to be Considered in Selecting of memory 18 the word size of the memory. The word Size refers to the number of Memory lift that any be dead world together at a time. 4,8,12,16,24,32.etc. are the word size offery le the number of memory lift that any be read with 4,612,6 24,32,etc. Ensure that the word size supported by the memory chip mathes with the dala by wilth of the processor!

> PLASH Hemory Comes in two wayor Garlants.

DNAND EXBNOR PLASH

NAND PLASH PSO HIGH-density low cost non-volution storage

Memory. NOR PLASH I'S less dense & Stigntly expensive. But

PE supports the Execute Proplace CXID technique for Program

execution.

The EEPROM data storage memory pg aslatable ay either Sext of Interface or parally guterface chipy.

Densors & Actuators

A sensor is a transducer devoice that converts energy from

one form to another for any measurement or control purpose

2) Actuators

Actuators is a form of transducer device Cylechanical or electrical which converts signals to corresponding physical Action (motion)-Actuators act as an opp device.

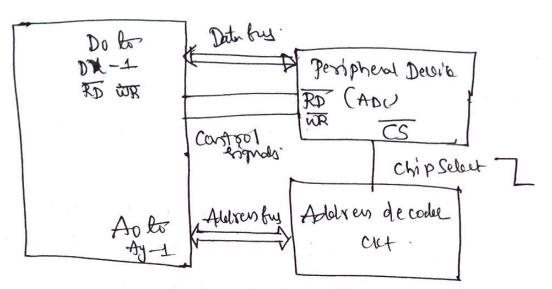

3) The Ilo Sursystem

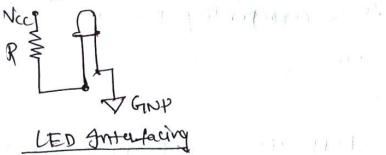

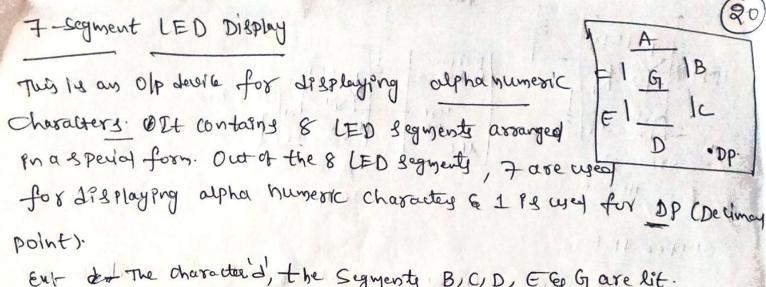

3) Light Emitting Diode (LED): This is an olp devoke for tolding Indication in any embedded system

- Signals Or situations. The examples are and acting the presence of power conditions like Dusto on, Battery low, Changing of battory for a battery Operated handless embedded devices.

- > CED 18 a PN Junctury dode and it watering Anode & Cathode.

The Anode is connected to any the terminal of the Supply yolf-ge,

Cathode is commerced to an Ne terminal of the Supply Nottage.

- The current flowing through the LED must be limited to a value felow the maximum current that it can conduct.

A resistor is used in sales for the power supply and the LED to sant the current through the LED

- Its Can be Interfaced to the part ply of a procurer Conti

and the port PRO dorver the LED. The port PIn Sources current. to the LED when the port PRO is at logic HAM (Logic 1)

- Protessor | Control er and the anode to the Supply voltage through a current limiting oner. The LED is ON when the port pry PS cet logic low (Logic'o').

- > In second opproach, the current 1s directly sourced by the power Supply of Port pin acts of the slower for current. Here the bright new for the LED.

The Number 4, the Segments F, G, BEFC are lif.

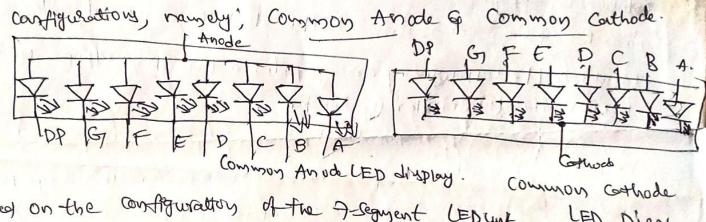

The 7- Segment LED Displays are avoilable in two different

> Based on the Configuration of the 7-segment LED LED Display

the LED segment of another or Cothodo is converted to the port of the

Processor | Controller M the order (A segment to the least significant

Port pin & DP segment to the most significant Port Ply

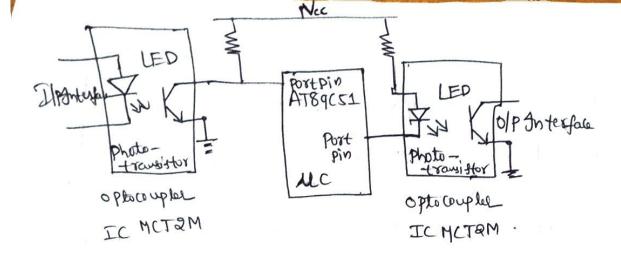

Opto couples:

Photo-transistor Ant

-> An optacoupler device

Opto couple Combines an LED & Phototoansistor en a sengle housing Characycy

An Optocoupler is used for suppressing Interference Py data Communication, cut I solutions High voltage separation, simultaneous separation & signer friction.

Optocouples can be used in lither ilp cuts or in olp cuts -

who have to be probable to the probable to the

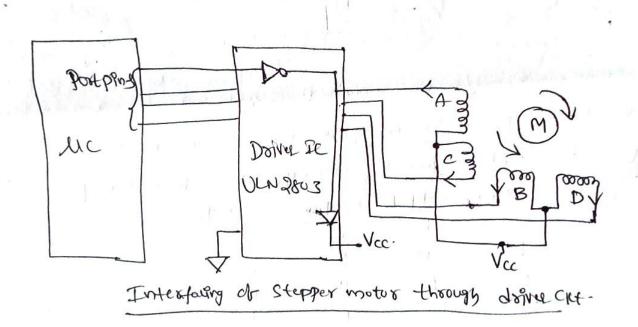

Stepper Motor

This also an electro-mechanical devoice which generates discrete displacement (motion) in response to de electrical elgnals. It differs from the mormal de motor in its operation. The demotor produces continuous totalism on applying de Voltage whereas a stepper motor produces discrete rotalism on response to the de Voltage applied to it:

Based on the coil winding arrangements, a two-phase Stepper Motor is classified. O unipolar 2 Bipolar

Unipolar. A unipolar Stepper motor contains two windings per phase. The direction of sotations (Charcoire or anticuarists) of a stepper motor is controlled by changing the directional current flow. Current In one direction flows through one coil of in the opposite direction flows through the other coil.

Supp.

Su

Motor

-> Coil & A Ge C Coursy current Pn Oppdite direction of for Phase I.

> Strol larly, BEED Carry Current PN Opposite directions for phase II.

Bipolar : Abppolar Stepper motor contains Single whating per phase. For reversing the motor rotation the current flow through the wordings be reversed dynamically.

The rotation of the stopper motor can be neversed by reversing the order Pn which the Coll 13 energised.

The current remirement for stepper motor is little high &

Hence the port pins of a Mc/ processor may not be able to

drive them directly. The supply bottoge required to operate stepper

motor boxies normally in the range sy to 24v.